# Low Latency Ifft Design for Ofdm Systems

Shreenidhi B K<sup>1</sup>, Roopashree<sup>2</sup>, Sharathchandra N R<sup>3</sup>

<sup>1</sup> (M.Tech. in VLSI Design and Embedded Systems, Sahyadri College of Engineering and Management, Adyar, Mangaluru, India)

<sup>2</sup>(Assistant Professor, Dept of Electronics and Communication Engineering, Sahyadri College of Engineering and Management, Adyar, Mangaluru, India)

<sup>3</sup>(Assistant Professor, Dept of Electronics and Communication Engineering, Sahyadri College of Engineering and Management, Adyar, Mangaluru, India)

Corresponding Author: Shreenidhi B K

**Abstract :** OFDM is a multi carrier modulation technique used in the various digital communication systems like 3G GSM, WiMAX, and LTE etc. The main advantage of this transmission technique is their hardiness to channel fading in wireless communication environment. Extensive connectivity, low latency and very high data transfer are the unique features of 5G networks. The digital audio Broadcasting, asynchronous digital subscriber line (ADSL) and high bit-rate digital subscriber line (HDSL) systems etc are some of the applications of OFDM in communication. Fast Fourier transform (FFT) and Inverse Fast Fourier Transform (IFFT) are two digital signal processing algorithm involved in OFDM system which are efficient for long instances in digital communication. The core processing block in an OFDM transmitter is the Inverse Fast Fourier Transform. For long instances, Single-Path Delay-Feedback (SDF) FFT architectures minimize required memory, which can dominate circuit area and power dissipation. The 8-point IFFT with radix-2 Single Delay Feedback algorithm have been analyzed for N=256 samples and incorporated in the design. **Keywords -** 3G GSM, WiMAX, LTE, ADSL, HDSL, Radix-2

Date of Submission: 18-06-2018

Date of acceptance: 04 -07-2018

## I. Introduction

Low latency Inverse Fast Fourier Transform (IFFT) is one of the design methods for OFDM systems which support full-duplex Frequency Division Duplex (FDD). To support full-duplex FDD OFDM systems means that transmission and reception are simultaneously performed. In order to reduce the IFFT output latency, we propose the reordering scheme of IFFT input data. By using the reordered IFFT input data, both the output latency and the memory size in the first stage of IFFT are significantly reduced. In this case, the FFT/IFFT processing can't be shared with one FFT/IFFT processor and therefore, they must be designed separately from each other. In the multi carrier systems like OFDM, IFFT/FFT is one of the key blocks in the physical layer implementation, since IFFT/FFT blocks require large amount of area, processing latency and power consumption. SDF approach based on radix-2 algorithm is frequently used for its low cost and high efficiency.

## 2.1. OFDM SYSTEMS

# **II.** Description

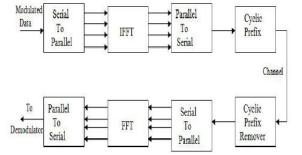

Orthogonal Frequency Division Multiplexing (OFDM) is adopted as standard in the many wireless communication applications since OFDM has the good performances of the systems under multipath fading channel. OFDM Signal transmission and reception using IFFT and FFT block is shown in figure1. In the OFDM systems, input data of the IFFT corresponding to guard band are assigned as null.

#### 2.2. IFFT

Low latency IFFT design method is proposed based on the fact that there are many null as an input data of IFFT. The common way to implement the inverse Fourier transform is by an IFFT algorithm. The equation (1) is the basic equation to calculate FFT.

$$X(k) = \sum_{n=1}^{N-1} x(n) e^{-j2\pi k n/N} , k = 0, ..., N-1^{(1)}$$

On the other hand, the equation (2) is used to calculate IFFT.

$$x(n) = \frac{1}{N} \sum_{n=1}^{N-1} X(k) e^{-j2\pi k n/N} , n = 0, ..., N-1^{(2)}$$

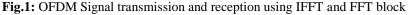

Where N is the transform size or the number of sample points in the data frame, X (k) is the frequency output of the FFT at k- th point where k=0, 1... N-1 and x (n) is the time sample at nth point with n=0, 1... N-1[1]. IFFT is a fast algorithm for IDFT operation. The twiddle factor (TW) W<sup>i</sup> means the e^j $2\pi k/N$ . The data flow for 8-point radix2 IFFT is shown in figure 2. In conventional radix-2 based SDF IFFT architecture, for the even cycles of  $N/2^i$  clock, input signals of *i*-th stage are bypassed at butterfly block and stored at the memory in each stage. For the odd cycles of  $N/2^i$  clock, butterfly operation compute at the same time and the addition outputs of butterfly are sent to next stage while the subtraction outputs of butterfly are stored at the memory in current stage.

#### 2.3. RADIX-2

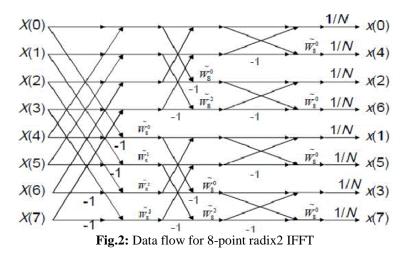

Radix-2 IFFT algorithm is used to reduce the order of computational complexity by decimating even and odd indices of input samples. IFFT architectures are mainly classified in two ways: Memory based architecture and pipelined based architecture. Popular pipelined architectures are based on radix-2 or radix-4 algorithms. Higher the radix, lower the computational complexity. Tradeoff for the selection of architecture is the requirement of length of IFFT for the particular application. Here Radix-2 Single Delay Feedback path is used. These provide memory feedback path to manage some butterfly outputs during each stage. This is one of the architecture for implementing IFFT on FPGA for multiple output orthogonal frequency division multiplexing. Radix-2 Single-path Delay Feedback [2] uses the registers more efficiently by storing the butterfly output in feedback shift registers. A single data stream goes through the multiplier at every stage. It has same number of butterfly units and multipliers as in R2MDC approach, but with much reduced memory requirement N-1registers. Its memory requirement is minimal. Where first N/2 input samples are stored in FIFO and operation starts when N/2+1st data is available at the input to the butterfly unit [3]. For designing N-stage pipelined FFT/IFFT. SFG shown in fig. 2 can be implemented using R2SDF. Block diagram for the same is shown in figure 3.

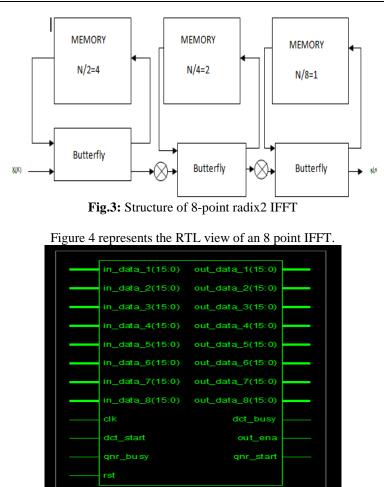

Fig.4: RTL view of an 8 point IFFT

## 2.4. POWER RESULT

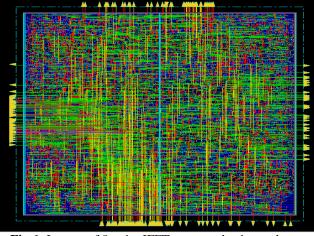

The power result shows the overall power performance of 8 point IFFT algorithm. The figure 5 shows the leakage power result for 8-IFFT algorithm. Layout generated using cadence is shown in figure 6.

| Instance                                                                      | Cells         | Leakage<br>Power(nW) | Dynamic<br>Power(nW) | Total<br>Power(nW) |   |

|-------------------------------------------------------------------------------|---------------|----------------------|----------------------|--------------------|---|

| dct2d                                                                         | 8392          | 2 323045.492         | 33402952.486         | 33725997.978       |   |

| Report Power _ 🗆 🗙                                                            |               |                      |                      |                    |   |

| Generated by: Encounter(R) RTL Compiler RC14.25 - v14.20-s046_1 (Aug 11 2015) |               |                      |                      |                    |   |

| Generated on: Jun 12 2018 17:07:46                                            |               |                      |                      |                    |   |

| Module: dct2d                                                                 |               |                      |                      |                    |   |

| Technology library: slow                                                      |               |                      |                      |                    |   |

| Operating conditions: slow (balanced_tree)                                    |               |                      |                      |                    |   |

| Wireload mode: enclosed                                                       |               |                      |                      |                    |   |

| Instance                                                                      | Cells Leakage | (nW) Internal        | (nW) Net (nW         | ) Switching (nW    |   |

| dct2d                                                                         |               |                      | 39.59 4321762.       |                    | - |

Fig.5: Analysis of power for 8 point IFFT in Xilinx and cadence

Fig.6: Layout of 8 point IFFT generated using cadence

## **III.** Conclusion

The 8-point Radix-2 IFFT is designed for OFDM system and the power result and timing is analyzed in Xilinx and Cadence.

#### References

- Ahmed Saeed, M.Elbably, G.Abdelfadeel, and M.I.Eladway, "Efficient FPGA Implementation of FFT/IFFT Processor", International Journal of Circuits, Systems and Signal Processing.

- R. Storn. Radix-2 FFT-pipeline architecture with reduced noise-to-signal ratio. IEE Proc.-Vis. Image Signal Process., 141(2):81–86, Apr. 1994

- [3]. Erling H. Wold "Pipelined and Parallel-pipelined FFT processor for VLSI Implementation" 0018-9340/84/0500- 0414\$01 .00 © 1984 IEEE

- [4]. Oh, J. Y. and Lim, M. S., "New radix-2 to the 4th power pipeline FFT processor", IEICE Trans. Electron., E88-C(8), 2005, pp.1740-1746.

- [5]. Cho, T. S. and L ee, H. H., "A high-speed low-complexity modified radix-25 FFT processor for high rate WPAN applications", IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 21(1), 2013, pp.187-191.

- [6]. Yu, C. and Yen, M., "Area-efficient 128- to 2048/1536-point pipeline FFT processor f or LTE and mobile W iMAX system", IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 23(9), 2015, pp.1793-1800.

- [7]. Tang, S. N., L iao. C. H. and Chang, T. Y., "An area and energy efficient multimode FFT processor for WPAN/WLAN/WMAN systems", IEEE J. Solid-State Circuits, 47(6), 2012, pp. 1491-1435.

- [8]. 3GPP LTE, "Evolved Universal Terrestrial Radio Access (E-UTRA); Base Station (BS) radio transmission and reception" 3GPP TS 36.104v13.3.0, 2016-03.

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) is UGC approved Journal with Sl. No. 4198, Journal no. 45125.

Lakshya Shahani. "Solution for Improving the Frequency of Operation of Metro Rail." IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) 13.3 (2018): 67-70.